D latch: Difference between revisions

From Rice Wiki

(Created page with "thumb|Figure 1. Schematic of a D latch The '''D latch''' is a direct upgrade from an SR latch. It has two inputs: (D)ata and (E)nabler. When ''E'' is activated, ''D'' is stored into the latch. When the enabler is deactivated, the circuit continues to latch the current value regardless of ''D''. = Clocked D latch = By connecting a clock to the enabler, you get a '''clocked D latch''' that is synchronized with the rest of the circuit. This is...") |

No edit summary |

||

| Line 10: | Line 10: | ||

The D-latch acts on level. This messes up the clock cycle. | The D-latch acts on level. This messes up the clock cycle. | ||

[[Category:Computer Architecture]] | |||

Latest revision as of 19:31, 17 May 2024

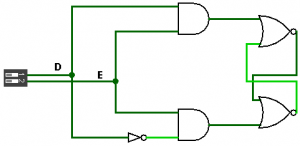

The D latch is a direct upgrade from an SR latch. It has two inputs: (D)ata and (E)nabler. When E is activated, D is stored into the latch. When the enabler is deactivated, the circuit continues to latch the current value regardless of D.

Clocked D latch

By connecting a clock to the enabler, you get a clocked D latch that is synchronized with the rest of the circuit. This is useful in ensuring that the D written to the .

An enabler can be integrated with AND gates. By fluctuating the enabler at set time intervals, we get a clocked D-latch.

Note that it is an abstraction and may be astable

The D-latch acts on level. This messes up the clock cycle.