SR latch: Difference between revisions

From Rice Wiki

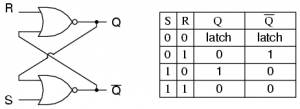

(Created page with "thumb|Figure 1. SR latch circuit and truth table The '''set-reset latch''' is a circuit that stores a value in a bistable circuit using two NOR gates. It is the fundamental building block for memory cells.") |

No edit summary |

||

| Line 1: | Line 1: | ||

[[File:SR Latch.png|thumb|Figure 1. SR latch circuit and truth table]] | [[File:SR Latch.png|thumb|Figure 1. SR latch circuit and truth table]] | ||

The '''set-reset latch''' is a circuit that stores a value in a [[bistable]] circuit using two NOR gates. It is the fundamental building block for memory cells. | The '''set-reset latch''' is a circuit that stores a value in a [[bistable]] circuit using two NOR gates. It is the fundamental building block for memory cells. | ||

An enabler can be integrated with AND gates. By fluctuating the enabler at set time intervals, we get a '''clocked D-latch'''. | |||

Note that it is an ''abstraction'' and may be [[astable]] | |||

[[Category:Computer Architecture]] | |||

Revision as of 15:42, 29 April 2024

The set-reset latch is a circuit that stores a value in a bistable circuit using two NOR gates. It is the fundamental building block for memory cells.

An enabler can be integrated with AND gates. By fluctuating the enabler at set time intervals, we get a clocked D-latch.

Note that it is an abstraction and may be astable